歡迎來深圳市立維創(chuàng)展科技有限公司官方網(wǎng)站!

-

首頁

Home -

關于我們

About -

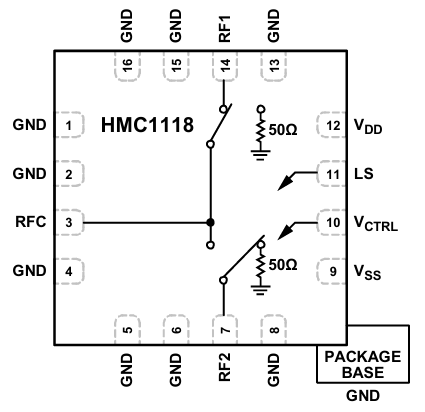

微波元器件

Microwave- AMCOM

- CUSTOM MMIC

- RF-LAMBDA

- QORVO

- MACOM

- SOUTHWEST

- NOVA射頻微波

- KRYTAR

- Aeroflex-API Tech

- Anaren

- Anritsu

- RADITEK

- North Hills

- Synergy微波

- WENTEQ

- MITEQ

- Marki

- RF-Labs

- ADI

- CREE

- UMS微波

- PULSAR微波

- MegaPhase

- JDSU光纖測試

- AMG-Microwave

- Ironwood

- Teledyne防務電子

- HEROTEK

- ARRA

- MCLI

- Leadway

- CERNEX

- Mi-Wave

- ATM Microwave(L-3)

- UTE Microwave

- NEL Frequency Controls

- API SAW Oscillators

- SemiGen

- KR Electronics

- MECA

- Electro-Photonics

- RLC Electronics

- JUPITER(Canada)

- ?IPP

-

電源模塊

Power -

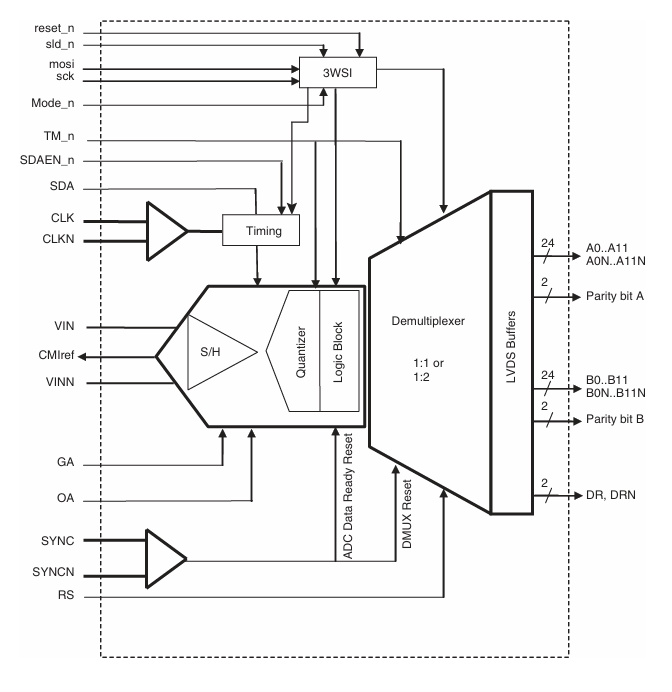

DAC | ADC芯片

DAC|ADC -

微處理器

MCU -

熱縮管

Heat Shrink Tubing -

自研產(chǎn)品

Leadway Prodcuts -

產(chǎn)品方案

Solution - 聯(lián)系我們

Contact