產(chǎn)品詳情介紹

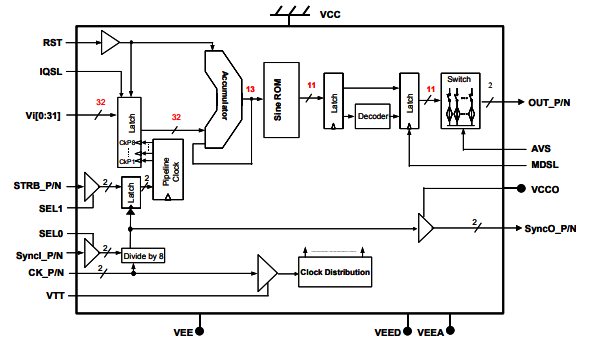

DS878是一種高速直接數(shù)字合成器(DDS),頻率調(diào)諧分辨率為32位,ROM相位分辨率為13位,DAC振幅分辨率為11位。DAC的模擬輸出可在正常保持模式(用于第一奈奎斯特波段)和歸零模式(用于第一、第二和第三奈奎斯特波段)操作之間選擇。在DAC的正常保持模式下,可產(chǎn)生高達(dá)1.8GHz附近的第一奈奎斯特波段(以3.6GHz的時(shí)鐘速率),或在DAC的歸零模式下產(chǎn)生高達(dá)5.4GHz的第三奈奎斯特波段。初始相位可以重置為零度開(kāi)始。該芯片有一對(duì)互補(bǔ)的模擬輸出,帶有50-∧的背面終端。輸出波形的頻率可由32個(gè)頻率控制位Vi[0:31]控制。DS878可接受差分時(shí)鐘輸入或單端時(shí)鐘輸入,具有50-∧片上后端終端和用戶定義的閾值。頻率分辨率位接受LVTTL或CMOS輸入電平。差分同步輸入SyncI_P/N為多個(gè)芯片應(yīng)用提供同步,并啟動(dòng)每個(gè)芯片準(zhǔn)備好接受頻率字輸入。同步選通輸入由內(nèi)部產(chǎn)生的除以8時(shí)鐘的過(guò)渡邊鎖存,這些時(shí)鐘也被發(fā)送到輸出引腳SyncO_P/N。SyncO_P/N可作為參考,將頻率字和頻閃信號(hào)輸入定時(shí)對(duì)準(zhǔn)同步到內(nèi)部除以8個(gè)時(shí)鐘,以正確鎖存。復(fù)位是異步的,以最小化模擬輸出有效性的時(shí)鐘延遲。對(duì)內(nèi)部定時(shí)進(jìn)行了優(yōu)化,以避免在頻率字轉(zhuǎn)換期間或重置后時(shí)鐘打滑。只需要一個(gè)-5V電源。

主要特點(diǎn)

?32位頻率調(diào)諧字

?13位ROM相位地址分辨率

?片上11位DAC

?時(shí)鐘頻率高達(dá)4.5 GHz

?模擬輸出可在正常保持格式和歸零格式之間選擇

?正弦波產(chǎn)生高達(dá)2.25 GHz的第一奈奎斯特頻帶用于正常保持模式或6.75 GHz第三奈奎斯特波段用于歸零模式。

?在4 GHz時(shí)鐘速率下,寬帶最差SFDR接近50 dBc(直流至2 GHz帶寬)

?帶50?背面終端的互補(bǔ)模擬波形輸出

?同步P/N同步多個(gè)芯片應(yīng)用

?SyncO_P/N為數(shù)據(jù)加載和同步選通信號(hào)提供參考。

?LVTTL/CMOS數(shù)字模式控制輸入

?異步復(fù)位(RST)引腳啟動(dòng)0相(IQSL=低)或90(IQSL=高)啟動(dòng)狀態(tài)

?選通輸入(STRB U P/N),以更新頻率字和DAC輸出頻率

?寬數(shù)據(jù)加載窗口允許DS878由存儲(chǔ)器、微控制器、FPGA或DSP芯片控制,以最快8個(gè)時(shí)鐘周期更新頻率字,而不會(huì)在頻率轉(zhuǎn)換期間出現(xiàn)時(shí)鐘滑動(dòng)或故障

?單個(gè)-5V電源的功耗為4.3W

?64針QFN 9x9封裝